# Fully abstract categorical semantics for digital circuits

---

George Kaye, David Sprunger and Dan Ghica

University of Birmingham

20 July 2022

ACT 2022

# Joint work with...

David Sprunger

Dan Ghica

# Introduction

Digital circuits are everywhere!

# Introduction

Digital circuits are everywhere!

How do we reason with them?

# Introduction

Generally by **simulation**

# Introduction

Generally by **simulation**

Reasoning in **software** is more **reduction-based**:

$$((\lambda x. \lambda y. x + y) 2) 5$$

# Introduction

Generally by **simulation**

Reasoning in **software** is more **reduction-based**:

$$((\lambda x. \lambda y. x + y) 2) 5 =_{\beta} (\lambda y. 2 + y) 5$$

# Introduction

Generally by **simulation**

Reasoning in **software** is more **reduction-based**:

$$((\lambda x. \lambda y. x + y) 2) 5 =_{\beta} (\lambda y. 2 + y) 5 =_{\beta} 2 + 5$$

# Introduction

Generally by simulation

Reasoning in software is more reduction-based:

$$((\lambda x. \lambda y. x + y) 2) 5 =_{\beta} (\lambda y. 2 + y) 5 =_{\beta} 2 + 5 =_{\eta} 7$$

# Introduction

Generally by simulation

Reasoning in software is more reduction-based:

$$((\lambda x. \lambda y. x + y) 2) 5 =_{\beta} (\lambda y. 2 + y) 5 =_{\beta} 2 + 5 =_{\eta} 7$$

We want an equational theory for digital circuits

# Syntax

---

# Combinational circuit components

# Combinational circuit components

## Values

-  false

-  true

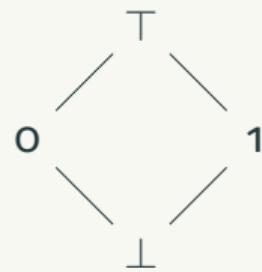

# Combinational circuit components

## Values

f false

t true

disconnected

short circuit

*(Belnap's four valued logic)*

# Combinational circuit components

## Values

-  false

-  true

-  disconnected

-  short circuit

*(Belnap's four valued logic)*

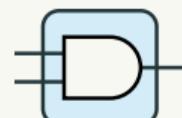

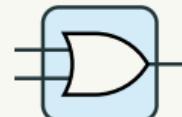

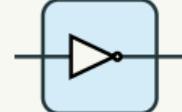

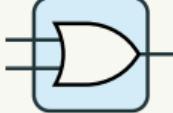

## Gates

-  AND gate

-  OR gate

-  NOT gate

# Combinational circuit components

| Values                              | Gates | Structure |

|-------------------------------------|-------|-----------|

|                                     |       |           |

|                                     |       |           |

|                                     |       |           |

|                                     |       |           |

| <i>(Belnap's four valued logic)</i> |       |           |

|                                     |       | AND gate  |

|                                     |       | OR gate   |

|                                     |       | NOT gate  |

# Combinational circuit components

| Values                              | Gates | Structure |

|-------------------------------------|-------|-----------|

|                                     |       |           |

|                                     |       |           |

|                                     |       |           |

|                                     |       |           |

| <i>(Belnap's four valued logic)</i> |       |           |

|                                     |       | AND gate  |

|                                     |       | OR gate   |

|                                     |       | NOT gate  |

|                                     |       | identity  |

|                                     |       | symmetry  |

# Combinational circuit components

| Values                                                                                          | Gates                                                                                      | Structure                                                                           |

|-------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------|

|  f             |                                                                                            | identity                                                                            |

|  t             |                                                                                            | symmetry                                                                            |

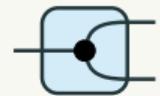

|  disconnected  |                                                                                            | fork                                                                                |

|  short circuit |                                                                                            |                                                                                     |

| <i>(Belnap's four valued logic)</i>                                                             |                                                                                            |                                                                                     |

|                                                                                                 |  AND gate |  |

|                                                                                                 |  OR gate  |  |

|                                                                                                 |  NOT gate |  |

# Combinational circuit components

| Values                                                                                          | Gates                                                                             | Structure                                                                           |

|-------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------|-------------------------------------------------------------------------------------|

|  false         |  | AND gate                                                                            |

|  true          |  | OR gate                                                                             |

|  disconnected  |  | NOT gate                                                                            |

|  short circuit |                                                                                   |                                                                                     |

| <i>(Belnap's four valued logic)</i>                                                             |                                                                                   |                                                                                     |

|                                                                                                 |                                                                                   |  |

|                                                                                                 |                                                                                   |  |

|                                                                                                 |                                                                                   |  |

|                                                                                                 |                                                                                   |  |

## Combinational circuit components

| Structure                                                                                       |          |

|-------------------------------------------------------------------------------------------------|----------|

| Values                                                                                          | Gates    |

|  f             | AND gate |

|  t             | OR gate  |

|  disconnected  | NOT gate |

|  short circuit |          |

| <i>(Belnap's four valued logic)</i>                                                             |          |

# Combinational circuit components

| Values                              | Gates | Structure |

|-------------------------------------|-------|-----------|

|                                     |       | identity  |

|                                     |       | symmetry  |

|                                     |       | fork      |

|                                     |       | join      |

|                                     |       |           |

|                                     |       |           |

|                                     |       |           |

| <i>(Belnap's four valued logic)</i> |       |           |

Light circuits

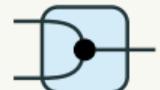

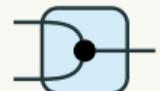

# Sequential circuit components

# Sequential circuit components

Delay

# Sequential circuit components

Delay

Feedback

# Sequential circuit components

Delay

Feedback

Dark circuits  may contain delay or feedback.

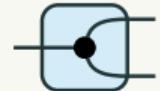

# Circuit morphisms

Morphisms in a **freely generated symmetric traced monoidal category**

# Semantics

---

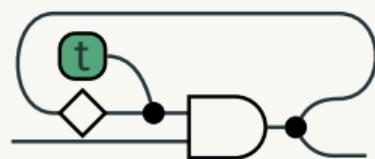

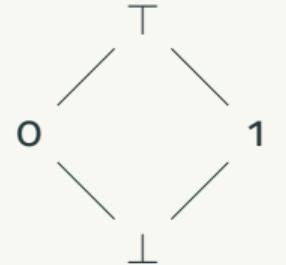

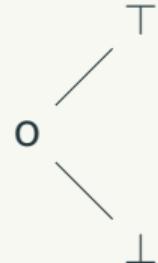

# Interpretation

Values are interpreted in a **lattice  $\mathbf{V}$** :

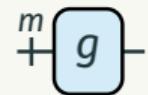

# Interpretation

monotone functions

$\bar{g}: \mathbf{V}^m \rightarrow \mathbf{V}$

# Interpretation

monotone functions

$$\bar{g}: \mathbf{V}^m \rightarrow \mathbf{V}$$

copy

$$x \mapsto (x, x)$$

# Interpretation

monotone functions

$$\bar{g}: \mathbf{V}^m \rightarrow \mathbf{V}$$

copy

$$x \mapsto (x, x)$$

join in the lattice

$$(x, y) \mapsto x \sqcup y$$

# Interpretation

monotone functions

$$\bar{g}: \mathbf{V}^m \rightarrow \mathbf{V}$$

copy

$$x \mapsto (x, x)$$

join in the lattice

$$(x, y) \mapsto x \sqcup y$$

discard

$$x \mapsto \bullet$$

## Stream functions

The semantics of circuits is that of **stream functions**.

## Stream functions

The semantics of circuits is that of **stream functions**.

A **stream**  $\mathbf{V}^\omega$  is an infinite sequence of values.

## Stream functions

The semantics of circuits is that of **stream functions**.

A **stream**  $\mathbf{V}^\omega$  is an infinite sequence of values.

A **stream function**  $f: (\mathbf{V}^m)^\omega \rightarrow (\mathbf{V}^n)^\omega$  consumes and produces streams.

## Causal stream functions

Not all stream functions correspond to sequential circuits...

## Causal stream functions

Not all stream functions correspond to sequential circuits...

Causal

Depends on past inputs

## Causal stream functions

Not all stream functions correspond to sequential circuits...

Causal

Depends on past inputs

Monotone

with respect to the lattice

# Causal stream functions

Not all stream functions correspond to sequential circuits...

Causal

Depends on past inputs

Monotone

with respect to the lattice

'Finite'

Specifies finite behaviours

# Causal stream functions

Not all stream functions correspond to sequential circuits...

Causal

Depends on past inputs

Monotone

with respect to the lattice

'Finite'

Specifies finite behaviours

## Theorem

*Every monotone causal stream function with 'finite behaviours' corresponds to a class of sequential circuits.*

# Equational reasoning

---

# Equality of circuits

When are two circuits equal?

## Equality of circuits

When are two circuits equal? When they have the same behaviour

# Equality of circuits

When are two circuits equal? When they have the same **behaviour**

# Equality of circuits

When are two circuits equal? When they have the same behaviour

When they have the same stream function

# Equality of circuits

When are two circuits equal? When they have the same behaviour

When they have the same stream function

Reasoning with streams is a pain.

We want to reason **equationally**: what equations do we need?

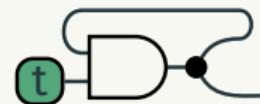

# Productivity

We want to reason **equationally**: what equations do we need?

First goal: **productivity**.

# Productivity

We want to reason **equationally**: what equations do we need?

First goal: **productivity**.

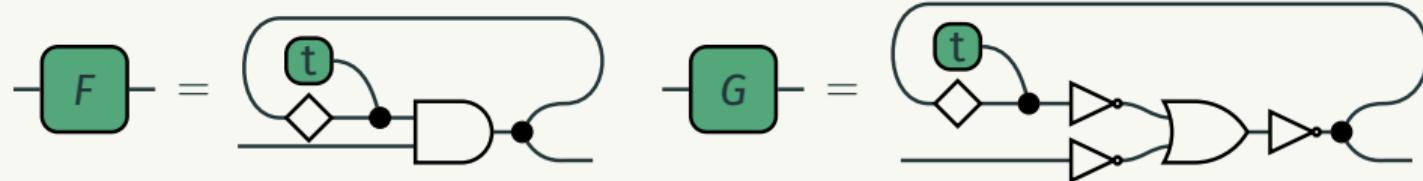

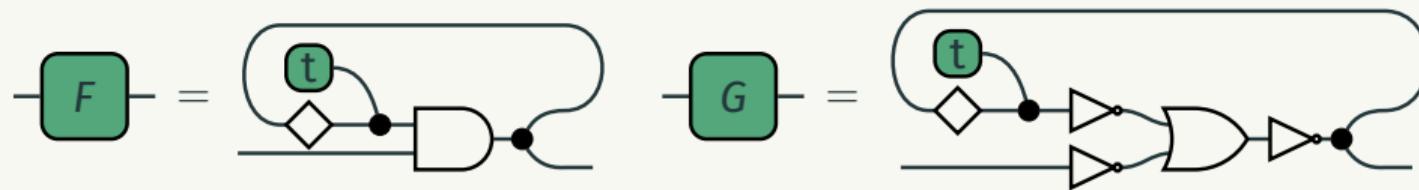

A closed circuit is **productive** if it is equal to an **instant value** and a **delayed subcircuit** under the equational theory.

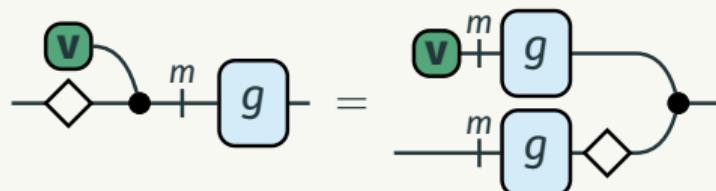

# Combinational equations

## Combinational equations

$$\text{v} \xrightarrow{m} g = \bar{g}(\text{v})$$

## Combinational equations

$$\begin{array}{ccc} \text{v} \xrightarrow{m} g & = & \bar{g}(\text{v}) \\ \text{v} \cup \text{w} & = & \text{v} \cup \text{w} \end{array}$$

## Combinational equations

$$\text{v} \xrightarrow{m} g = \bar{g}(\text{v}) = \text{v} \sqcup \text{w}$$

$$\text{v} \xrightarrow{m} F = F \xrightarrow{m} \text{v} \xrightarrow{n} \text{w}$$

## Combinational equations

$$\text{v} \xrightarrow{m} g = \bar{g}(\text{v})$$

$$v \sqcup w = v \sqcup w$$

$$\begin{matrix} m \\ + \end{matrix} \xrightarrow{n} F = \begin{matrix} m \\ - \end{matrix} \xrightarrow{n} F \quad \begin{matrix} m \\ + \end{matrix} \xrightarrow{n} F = \begin{matrix} m \\ + \end{matrix}$$

## Combinational equations

$$\text{v} \xrightarrow{m} g = \bar{g}(\text{v}) \quad \begin{array}{c} \text{v} \\ \text{w} \end{array} \text{---} \bullet = \text{v} \sqcup \text{w}$$

$$\begin{array}{c} m \\ + \end{array} F \begin{array}{c} n \\ + \end{array} \bullet = \begin{array}{c} m \\ + \end{array} \text{---} \begin{array}{c} n \\ + \end{array} F \quad \begin{array}{c} m \\ + \end{array} F \begin{array}{c} n \\ + \end{array} \bullet = \begin{array}{c} m \\ + \end{array}$$

$$\bullet \text{---} \bullet = \text{---} = \text{---} \bullet \quad \bullet \text{---} \bullet = \text{---} = \text{---} \bullet$$

## Combinational equations

$$\text{v} \xrightarrow{m} g = \bar{g}(\text{v}) \quad \text{v} \text{ and } \text{w} = \text{v} \sqcup \text{w}$$

$$\text{v} \xrightarrow{m} F \xrightarrow{n} \text{v} = \text{v} \quad \text{v} \xrightarrow{m} F \xrightarrow{n} \text{v} = \text{v}$$

$$\text{v} = \text{v} = \text{v} = \text{v} = \text{v}$$

These reduce any **closed combinational circuit**  $\text{v} \xrightarrow{m} F \xrightarrow{n} \text{v}$  to some  $\text{v} \xrightarrow{n} \text{v}$ .

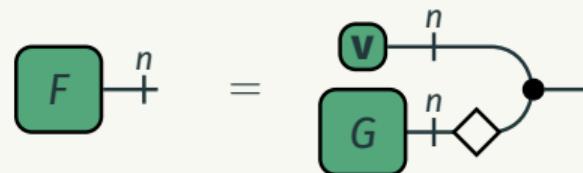

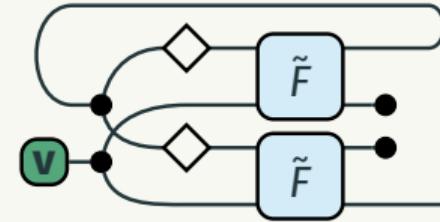

## Sequential equations

$$\bullet \text{---} \diamond \text{---} = \bullet \text{---}$$

## Sequential equations

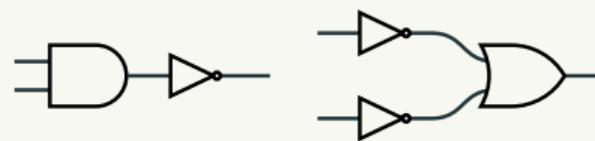

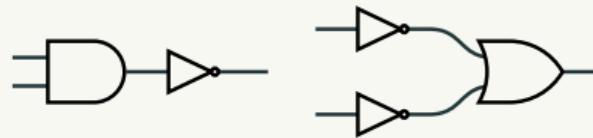

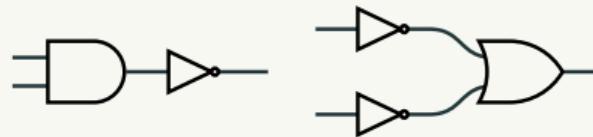

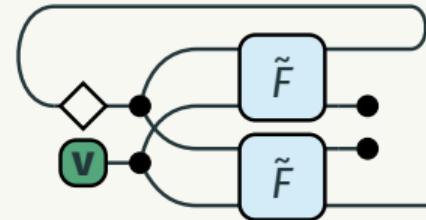

## Non delay-guarded feedback

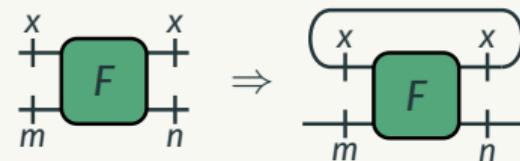

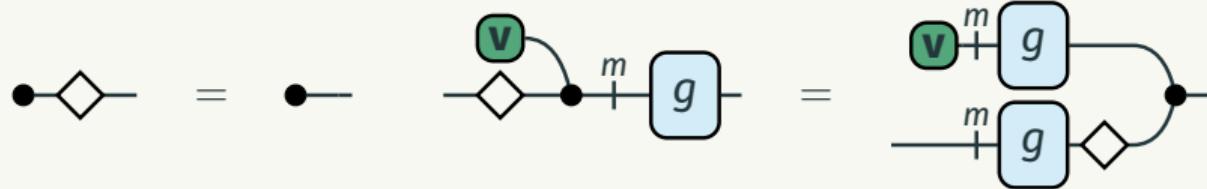

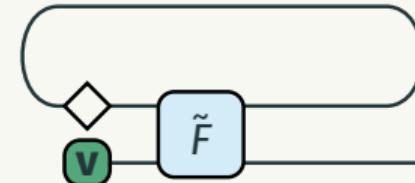

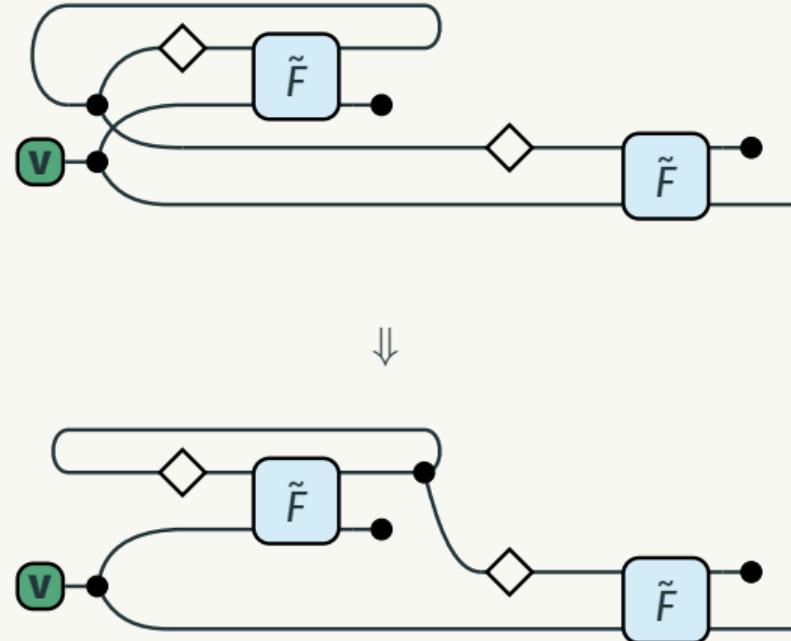

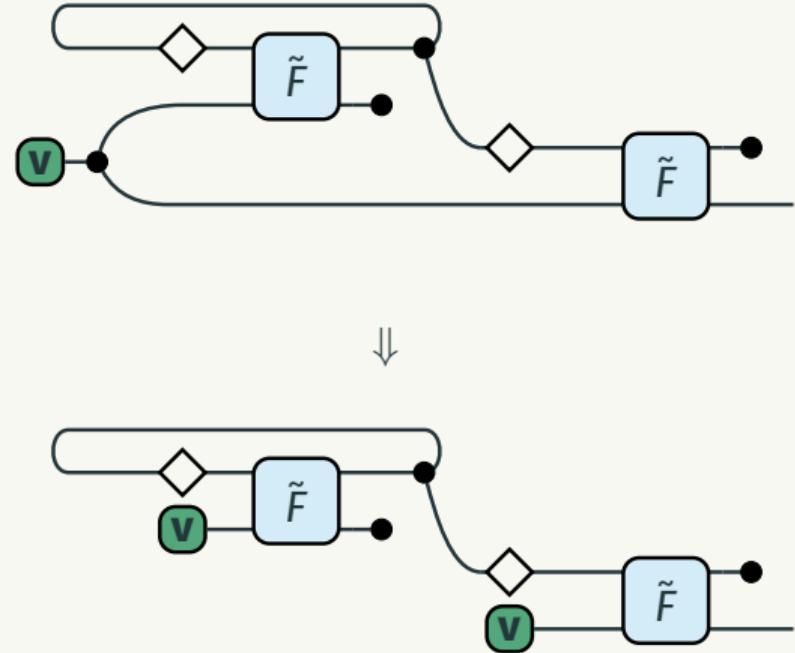

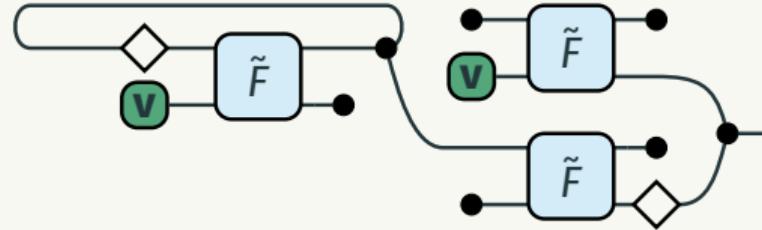

How do we deal with something like this?

## Non delay-guarded feedback

How do we deal with something like this?

We need a way to eliminate **non delay-guarded feedback**.

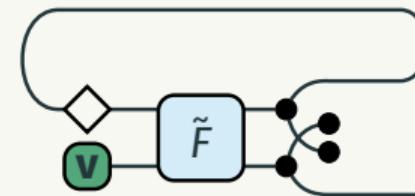

## Non delay-guarded feedback

## Non delay-guarded feedback

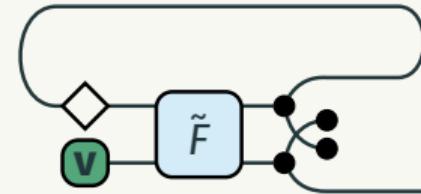

Our gates are **monotonic**, so they must have a **least fixed point**...

## Non delay-guarded feedback

Our gates are **monotonic**, so they must have a **least fixed point**...

Because the value set **V** is finite, we can always find this fixpoint!

## Non delay-guarded feedback

In **V**, the length of the longest chain is **2**...

## Non delay-guarded feedback

In **V**, the length of the longest chain is **2**...

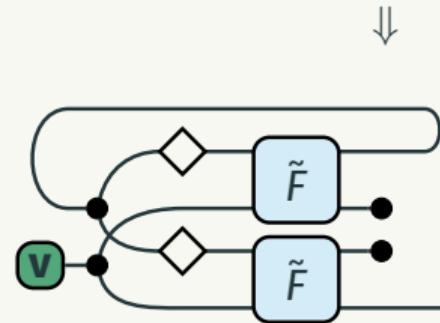

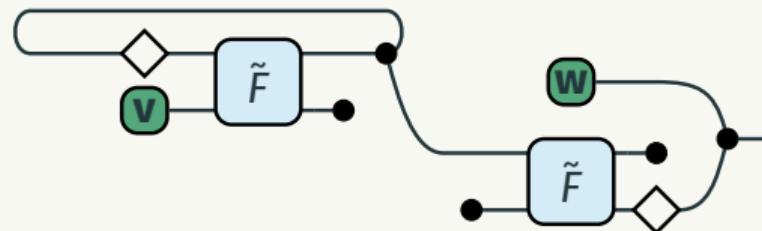

# Productivity

We want

# Productivity

Axioms of STMCs

# Productivity

Eliminating 'instant feedback'

# Productivity

Axioms of STMCs

# Productivity

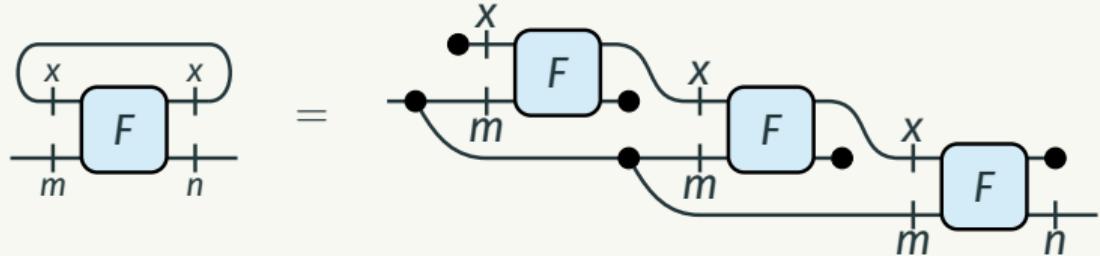

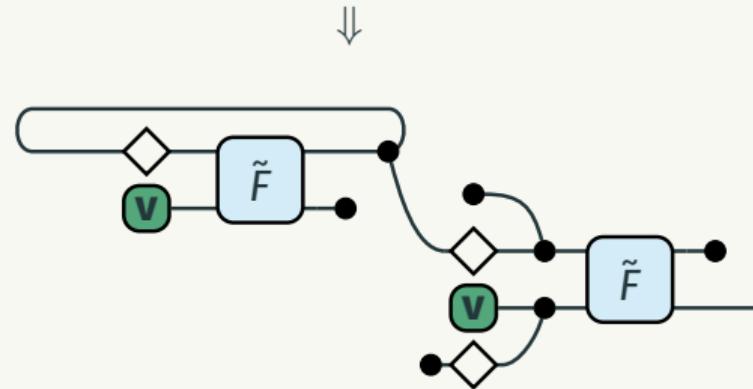

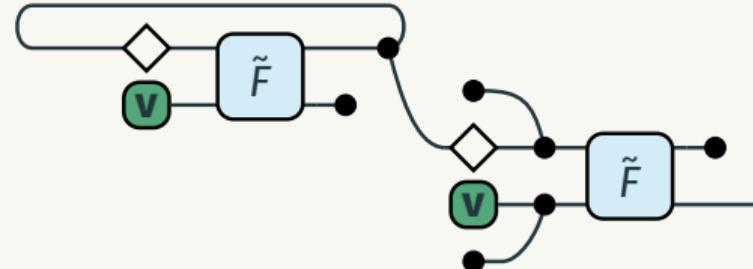

↓

# Productivity

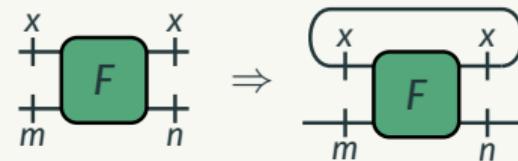

$$\begin{array}{c} m \\ + \end{array} \begin{array}{c} F \\ \square \end{array} \begin{array}{c} n \\ + \end{array} = \begin{array}{c} m \\ + \end{array} \begin{array}{c} F \\ \square \end{array} \begin{array}{c} n \\ + \end{array} \begin{array}{c} m \\ + \end{array} \begin{array}{c} F \\ \square \end{array} \begin{array}{c} n \\ + \end{array}$$

↓

# Productivity

$$\begin{array}{c} m \\ + \end{array} \begin{array}{c} F \\ \square \end{array} \begin{array}{c} n \\ + \end{array} = \begin{array}{c} m \\ + \end{array} \begin{array}{c} F \\ \square \end{array} \begin{array}{c} n \\ + \end{array} \begin{array}{c} m \\ + \end{array} \begin{array}{c} F \\ \square \end{array} \begin{array}{c} n \\ + \end{array}$$

# Productivity

Axioms of STMCs

# Productivity

Axioms of STMCs

# Productivity

$$m \begin{array}{c} + \\ \text{---} \\ F \\ \text{---} \\ + n \end{array} = \begin{array}{c} m \begin{array}{c} + \\ \text{---} \\ F \\ \text{---} \\ + n \end{array} \\ \text{---} \\ m \begin{array}{c} + \\ \text{---} \\ F \\ \text{---} \\ + n \end{array} \end{array}$$

# Productivity

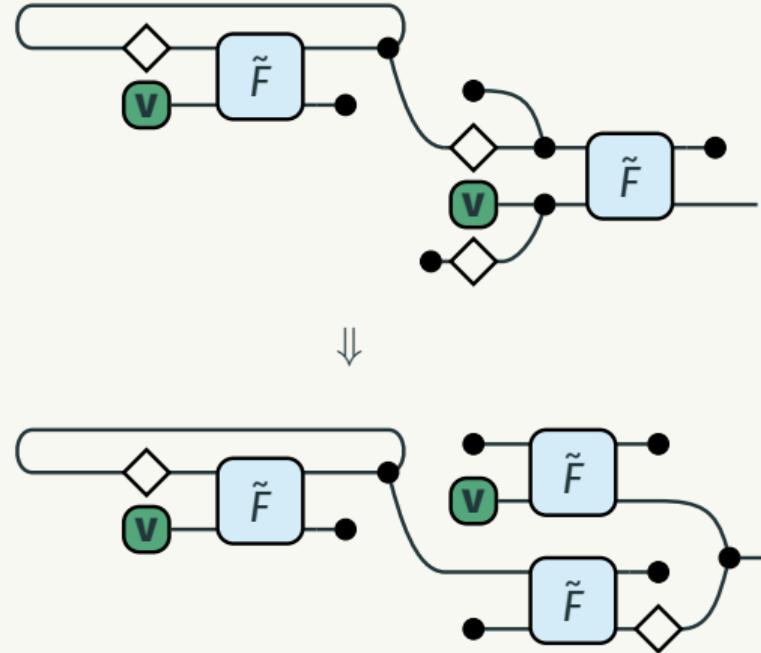

↓

# Productivity

$$\bullet - = \bullet \diamond$$

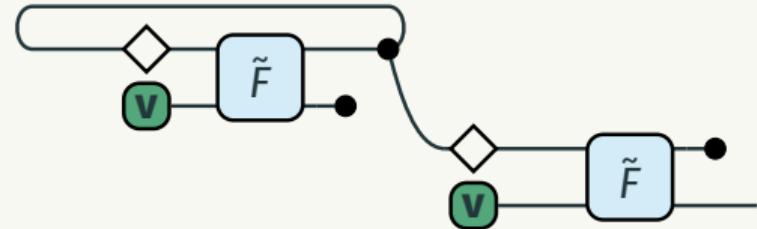

# Productivity

# Productivity

Combinational circuit equations

# Productivity

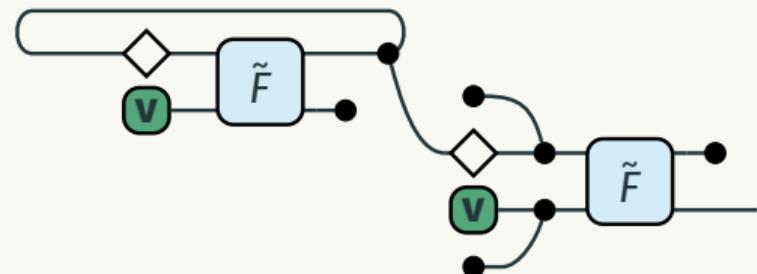

Tidying up

# Productivity

Any circuit has an **instantaneous value** and a **delayed subcircuit**.

# Productivity

Any circuit has an **instantaneous value** and a **delayed subcircuit**.

These values are the elements of the corresponding stream!

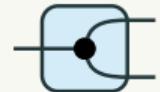

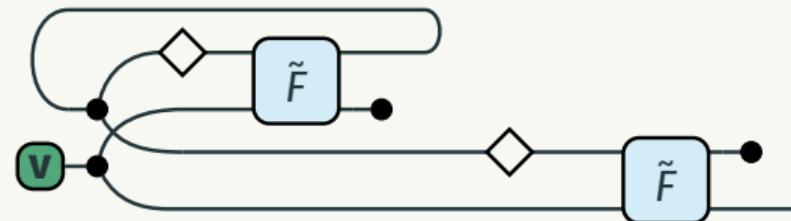

## Open circuits

We still cannot translate between **open** circuits with the same behaviour.

## Open circuits

We still cannot translate between **open** circuits with the same behaviour.

## Open circuits

We still cannot translate between **open** circuits with the same behaviour.

When do two circuits have the **same stream**?

## Open circuits

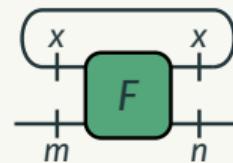

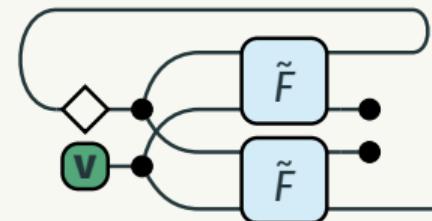

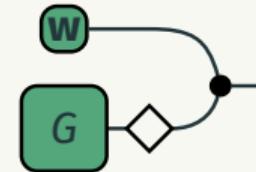

We can think of circuits as **state machines**:

# Open circuits

We can think of circuits as **state machines**:

# Open circuits

We can think of circuits as **state machines**:

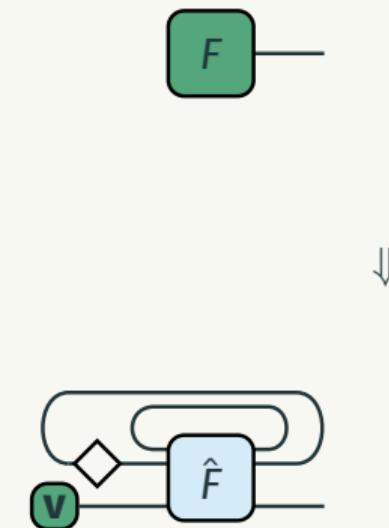

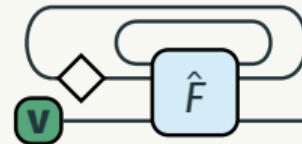

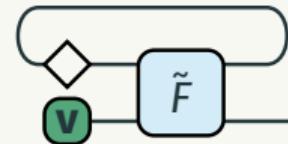

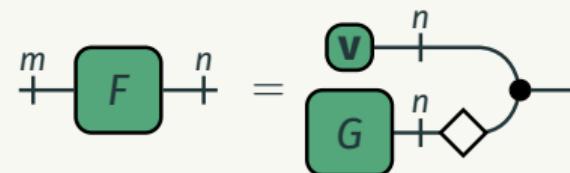

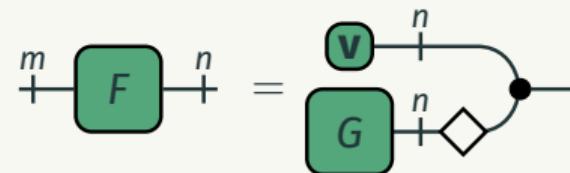

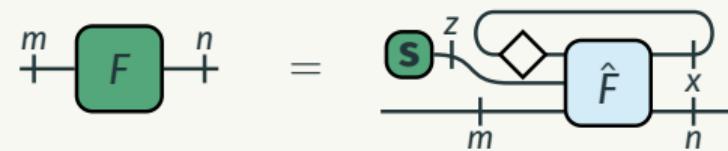

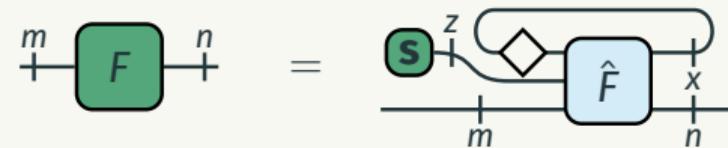

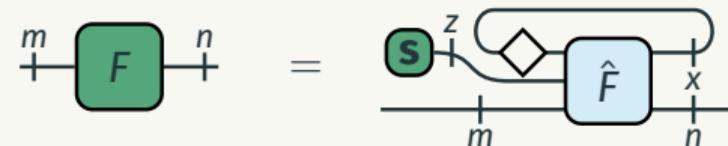

The circuit  produces the **state transition** and **output** of  $\begin{array}{c} m \\ + \end{array} \begin{array}{c} F \\ \boxed{F} \end{array} \begin{array}{c} n \\ + \end{array}$ .

# Open circuits

We can think of circuits as **state machines**:

The circuit  $\hat{F}$  produces the **state transition** and **output** of  $F$ .

**Idea:** for all **accessible states**, if the **outputs** are equal then the **original circuits** are equal under the equational theory.

(cf. Mealy machine bisimulation)

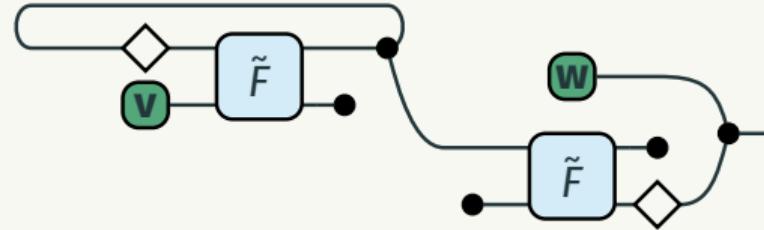

## Theorem

$\overset{m}{+} \boxed{F} \overset{n}{+} = \overset{m}{+} \boxed{G} \overset{n}{+}$  if and only if their streams are equal.

## Proof.

□

## Theorem

$\overset{m}{+} \boxed{F} \overset{n}{+} = \overset{m}{+} \boxed{G} \overset{n}{+}$  if and only if their streams are equal.

## Proof.

□

## Theorem

$$\begin{array}{c} m \\ + \end{array} \boxed{F} \begin{array}{c} n \\ + \end{array} = \begin{array}{c} m \\ + \end{array} \boxed{G} \begin{array}{c} n \\ + \end{array} \text{ if and only if their streams are equal.} \end{array}$$

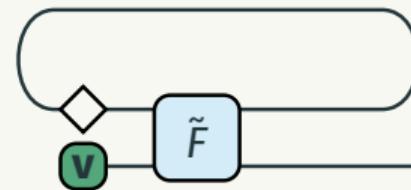

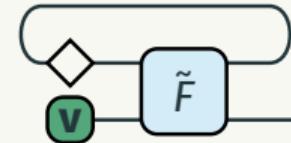

## Proof.

$$\begin{array}{c} m \\ + \end{array} \boxed{F} \begin{array}{c} n \\ + \end{array} = \boxed{S} \begin{array}{c} z \\ \downarrow \end{array} \begin{array}{c} \diamond \\ \downarrow \end{array} \boxed{\hat{F}} \begin{array}{c} x \\ \downarrow \end{array} \begin{array}{c} n \\ + \end{array} = \boxed{r} \begin{array}{c} w \\ \downarrow \end{array} \begin{array}{c} \diamond \\ \downarrow \end{array} \boxed{\hat{G}} \begin{array}{c} y \\ \downarrow \end{array} \begin{array}{c} n \\ + \end{array} = \begin{array}{c} m \\ + \end{array} \boxed{G} \begin{array}{c} n \\ + \end{array} \end{array}$$

□

## Theorem

$$\begin{array}{c} m \\ + \end{array} \boxed{F} \begin{array}{c} n \\ + \end{array} = \begin{array}{c} m \\ + \end{array} \boxed{G} \begin{array}{c} n \\ + \end{array} \text{ if and only if their streams are equal.} \end{array}$$

## Proof.

$$\begin{array}{c} m \\ + \end{array} \boxed{F} \begin{array}{c} n \\ + \end{array} = \boxed{S} \begin{array}{c} z \\ \diamond \\ m \end{array} \boxed{\hat{F}} \begin{array}{c} x \\ n \end{array} = \boxed{r} \begin{array}{c} w \\ \diamond \\ m \end{array} \boxed{\hat{G}} \begin{array}{c} y \\ n \end{array} = \begin{array}{c} m \\ + \end{array} \boxed{G} \begin{array}{c} n \\ + \end{array} \end{array}$$

□

## Conclusion

We have presented a **categorical framework** for sequential circuits

## Conclusion

We have presented a **categorical framework** for sequential circuits

Circuits have semantics as **stream functions**

## Conclusion

We have presented a **categorical framework** for sequential circuits

Circuits have semantics as **stream functions**

It is easier to reason **equationally**

## Conclusion

We have presented a **categorical framework** for sequential circuits

Circuits have semantics as **stream functions**

It is easier to reason **equationally**

We have **full abstraction**: a correspondence between syntactic and semantic

## Conclusion

We have presented a **categorical framework** for sequential circuits

Circuits have semantics as **stream functions**

It is easier to reason **equationally**

We have **full abstraction**: a correspondence between syntactic and semantic

Next step: refine the **rewriting system**